VLSI CAD Part II: Layout

FREE

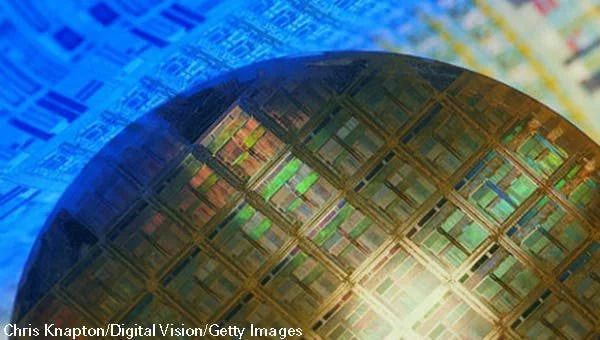

You should complete the VLSI CAD Part I: Logic course before beginning this course. A modern VLSI chip is a remarkably complex beast: billions of transistors, millions of logic gates deployed for computation and control, big blocks of memory, embedded blocks of pre–designed functions designed by third parties (called “intellectual property” or IP blocks). How do people manage to design these complicated chips? Answer: a sequence of computer aided design (CAD) tools takes an abstract description of the chip, and refines it step–wise to a final design. This class focuses on the major design tools used in the creation of an Application Specific Integrated Circuit (ASIC) or System on Chip (SoC) design. Our focus in this part of the course is on the key logical and geometric representations that make it possible to map from logic to layout, and in particular, to place, route, and evaluate the timing of large logic networks. Our goal is for students to understand how the tools themselves work, at the level of their fundamental algorithms and data structures. Topics covered will include: technology mapping, timing analysis, and ASIC placement and routing. Recommended Background: Programming experience (C, C++, Java, Python, etc.) and basic knowledge of data structures …

Instructor Details

Courses : 2

Specification: VLSI CAD Part II: Layout

|

19 reviews for VLSI CAD Part II: Layout

Add a review Cancel reply

This site uses Akismet to reduce spam. Learn how your comment data is processed.

| Price | Free |

|---|---|

| Provider | |

| Duration | 12 hours |

| Year | 2017 |

| Level | Intermediate |

| Language | English |

| Certificate | Yes |

| Quizzes | Yes |

FREE

BHARATH K –

Amazing!!!

Kanishka S –

Excellent course, very helpful!

Pankaj M –

Very good to learn algorithms!

Mohammad H –

It was a great experience, really great lecturer without exaggerating, but the programming assignment 3 (which is optional) was totally a nightmare, I wrote about 1000 line of code to do both the essential and the extra parts, but not yet. I hope there was another course for design using HDL like Verilog or System Verilog.

Akash L –

Great basic overview of the core design principles for EDA

Robin M –

As a software developer without background in EE I have always wondered how Boolean logic is turned into actual physical hardware, and this course (along with its predecessor “VLSI CAD Part I: Logic”) has answered all my questions.

Shaanvi M –

very helpful, and delivered very well.

Navdeep D –

Good

V V R R –

THANK YOU

K L N A –

EXCELLENT

Arvind –

no comments

HARSH V P –

excelllent

Shresth N –

very nice and challenging

Arighna D –

Excellent.

Divyang T –

A very good course for students who want to have an understanding of Physical Design process in semiconductor industry. I want to thank professor for making this course so informative. A must for people looking to dive deep into Electronics.

kanishk j –

Good course content and prof. ‘s teaching method makes it easy to comprehend quite quickly.

Md. F K –

Another interesting and well taught course.

Devansh S –

An awesome course which I can put to great use in my academic life.

SIDDEM M –

good